# **WOLFSON®** microelectronics

# WM8777

# 24-bit, 192kHz AV Receiver on-a-Chip

## DESCRIPTION

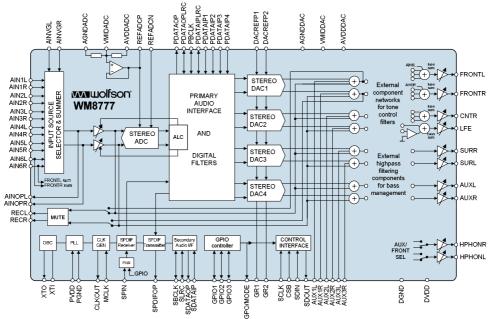

The WM8777 is a high performance, multi-channel audio codec. The WM8777 is ideal for surround sound processing applications for home hi-fi, automotive and other audio visual equipment. A S/PDIF transceiver with 4-channel input mux is included. Analogue domain bass management processing, and front channel analogue tone control facilities are provided.

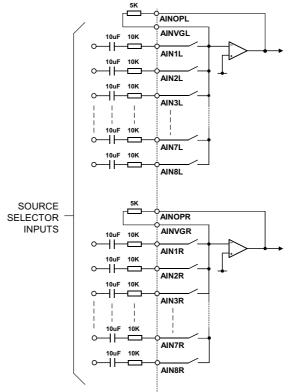

A stereo 24-bit multi-bit sigma delta ADC is used with a six stereo channel input selector. Each channel has analogue domain mute and programmable gain control. Sampling rates from 8kHz to 192kHz are supported.

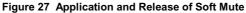

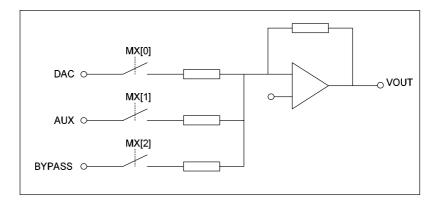

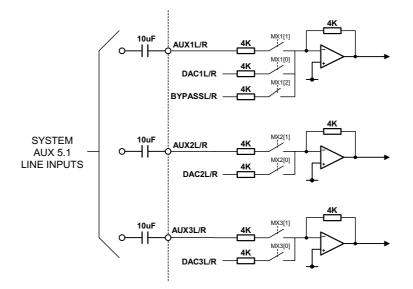

Four stereo 24-bit multi-bit sigma delta DACs are provided, which may be used to support up to 7.1 channel operation. If preferred, 5.1 operation may be chosen, with the spare stereo DAC used to support an Aux remote room. Sampling rates from 8kHz to 192kHz are supported. Each DAC channel has independent digital volume and mute control. A set of input multiplexors allows switching of an external 5.1 analogue input, or bypass channel stereo analogue input into the signal path. The front channel analogue signals may be looped out of the chip prior to each master volume control, and external filtering applied in order to select treble and bass filter characteristics. Adjustment of tone controls is then achieved using on-chip gain adjust amplifiers, addressed via the control interface. Analogue bass management support is provided, plus analogue stereo mixdown options.

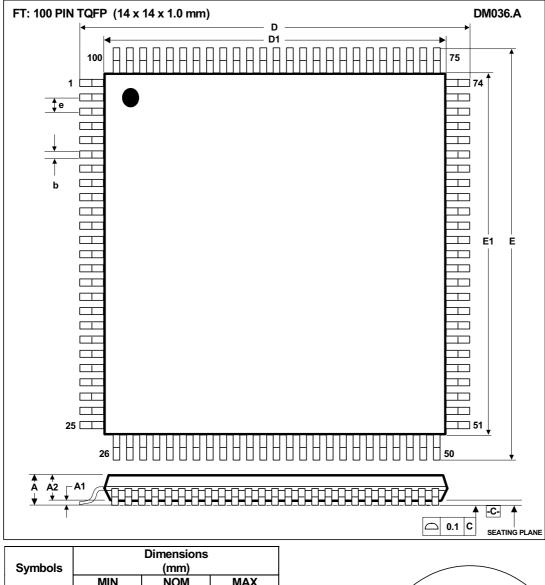

The device is controlled via a serial interface giving access to all features including channel selection, volume controls, tone controls, mutes, de-emphasis and power management facilities. The device is available in a 100-pin LQFP package.

# **FEATURES**

- AV receiver on-a-chip with 8 DACs and 2 ADCs

- Integrated S/PDIF/IEC60958/AES3 transceiver

- Analogue Bass Management and stereo mixdown support

- Analogue tone controls for front 3 channels

- Master volume control on each DAC channel with gain range of +20dB to -100dB in 1dB steps

- Audio Performance

- 108dB SNR ('A' weighted @ 48kHz) DAC

- 102dB SNR ('A' weighted @ 48kHz) ADC

- 110dB SNR ('A' weighted) Analogue volume control

- DAC Sampling Frequency: 8KHz 192kHz

- ADC Sampling Frequency: 8KHz 192kHz

- 3-Wire SPI or 2-wire MPU Serial Control Interface with readback.

- Master or Slave Clocking Mode

- Programmable Format Audio Data Interface Modes

- Four Independent stereo DAC outputs with independent digital volume controls

- Integrated Stereo headphone amplifier with source select

- 5.1 channel analogue input prior to the tone controls, bass management and stereo mixdown functions.

- Six stereo input ADC mux with analogue gain adjust from +24dB to -21dB in 0.5dB steps

- 5V Analogue, 2.7V to 3.6V Digital supply Operation

### APPLICATIONS

• Surround Sound AV Processors and Hi-Fi systems

# TABLE OF CONTENTS

| DESCRIPTION                                     | 1    |

|-------------------------------------------------|------|

| FEATURES                                        | 1    |

| APPLICATIONS                                    | 1    |

| TABLE OF CONTENTS                               | 2    |

| PIN CONFIGURATION                               |      |

| ORDERING INFORMATION                            | -    |

| PIN DESCRIPTION                                 |      |

| ABSOLUTE MAXIMUM RATINGS                        |      |

| RECOMMENDED OPERATING CONDITIONS                |      |

| ELECTRICAL CHARACTERISTICS                      |      |

| TERMINOLOGY                                     |      |

| SUPPLY CURRENT                                  |      |

| DEVICE DESCRIPTION                              |      |

|                                                 |      |

| INTRODUCTION<br>ANALOGUE TONE CONTROLS          |      |

| BASS MANAGEMENT                                 |      |

| HEADPHONE OUTPUT                                |      |

| OUTPUT POWERDOWN                                |      |

| DIGITAL AUDIO INTERFACE ROUTING OPTIONS         |      |

| CONTROL INTERFACE OPERATION                     |      |

| CONTROL INTERFACE TIMING                        |      |

| MASTER CLOCK                                    |      |

| AUDIO SAMPLING RATES AND AUDIO INTERFACES       |      |

| AUDIO INTERFACE FORMATS                         |      |

| DIGITAL AUDIO INTERFACE CONTROL REGISTERS       |      |

| POWERDOWN MODES                                 | . 39 |

| MASTER CLOCK AND PHASE LOCKED LOOP              |      |

| S/PDIF TRANSCEIVER FEATURES                     | . 45 |

| S/PDIF TRANSMITTER                              | . 47 |

| S/PDIF RECEIVER                                 |      |

| DAC CONTROL REGISTERS                           |      |

| OUTPUT SELECT AND ENABLE CONTROL                |      |

| ADC CONTROL REGISTERS                           |      |

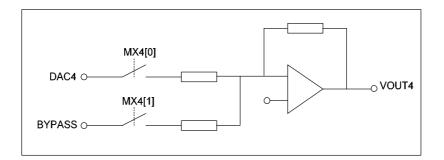

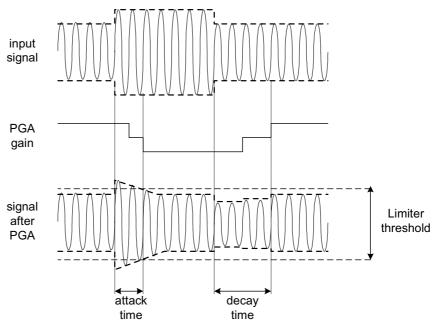

| LIMITER / AUTOMATIC LEVEL CONTROL (ALC)         | . 68 |

| SOFTWARE REGISTER RESET                         |      |

| REGISTER MAP                                    |      |

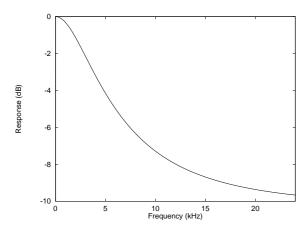

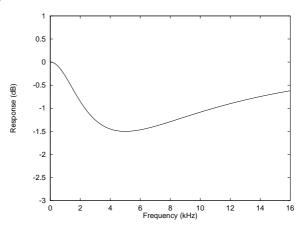

| DIGITAL FILTER CHARACTERISTICS                  |      |

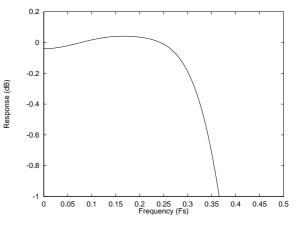

| DAC FILTER RESPONSES                            | .95  |

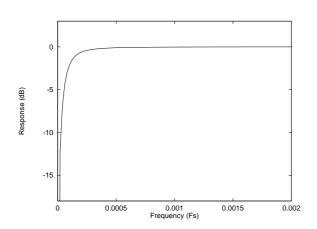

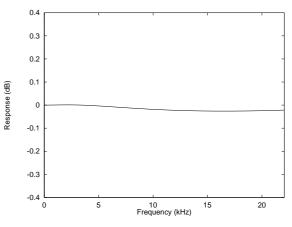

| ADC HIGH PASS FILTER                            |      |

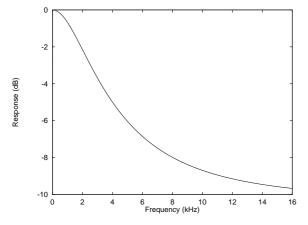

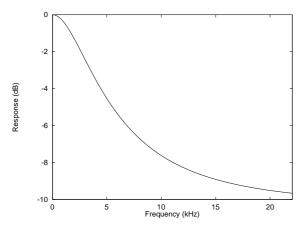

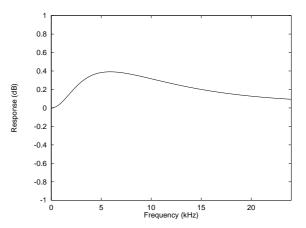

| DIGITAL DE-EMPHASIS CHARACTERISTICS             |      |

| APPLICATIONS INFORMATION                        | .98  |

| EXTERNAL ANALOGUE INPUT CIRCUIT CONFIGURATION   |      |

| EXTERNAL S/PDIF INPUT CIRCUIT CONFIGURATION     |      |

| RECOMMENDED ANALOGUE OUTPUT EXTERNAL COMPONENTS |      |

| IMPORTANT NOTICE                                |      |

| ADDRESS:                                        | 102  |

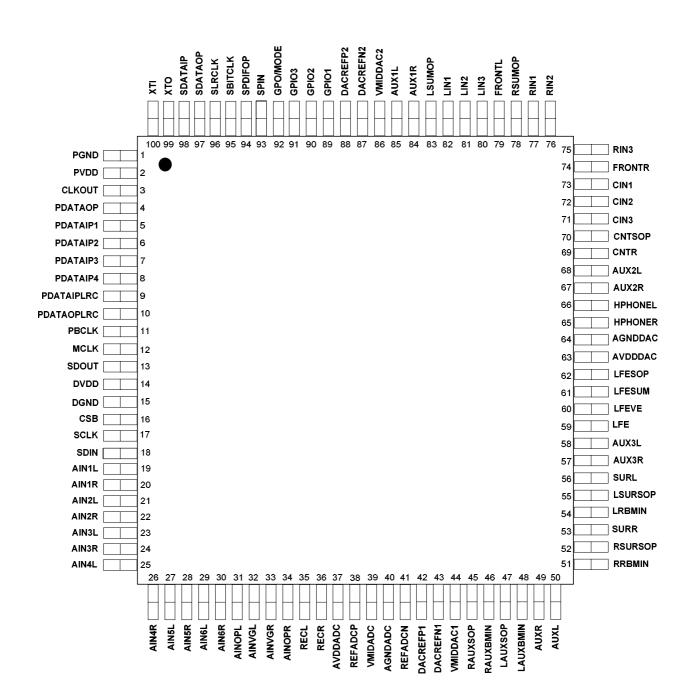

**PIN CONFIGURATION**

## **ORDERING INFORMATION**

| DEVICE       | TEMPERATURE<br>RANGE | PACKAGE      | MOISTURE SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |  |

|--------------|----------------------|--------------|-------------------------------|-------------------------------|--|

| WM8777SEFT/V | -25°C to +85°C       | 100-pin TQFP | MSL3                          | 240°C                         |  |

# **PIN DESCRIPTION**

| PIN | NAME       | TYPE                 | DESCRIPTION                                                                               |

|-----|------------|----------------------|-------------------------------------------------------------------------------------------|

| 1   | PGND       | Supply               | PLL ground supply                                                                         |

| 2   | PVDD       | Supply               | PLL positive supply                                                                       |

| 3   | CLKOUT     | Digital output       | PLL output or crystal oscillator output                                                   |

| 4   | PDATAOP    | Digital output       | Primary Audio Interface data output (ADC)                                                 |

| 5   | PDATAIP1   | Digital Input        | Primary Audio Interface data input 1 (DAC1)                                               |

| 6   | PDATAIP2   | Digital Input        | Primary Audio Interface data input 2 (DAC2)                                               |

| 7   | PDATAIP3   | Digital Input        | Primary Audio Interface data input 3 (DAC3)                                               |

| 8   | PDATAIP4   | Digital Input        | Primary Audio Interface data input 4 (DAC4)                                               |

| 9   | PDATAIPLRC | Digital input/output | DAC left/right word clock                                                                 |

| 10  | PDATAOPLRC | Digital input/output | ADC left/right word clock                                                                 |

| 11  | PBCLK      | Digital input/output | ADC and DAC audio interface bit clock                                                     |

| 12  | MCLK       | Digital input/output | Master DAC and ADC clock; 128, 192, 256, 384, 512, 768fs or 1152fs (fs = word clock freq) |

| 13  | SDOUT      | Digital output       | Serial interface output data                                                              |

| 14  | DVDD       | Supply               | Digital positive supply                                                                   |

| 15  | DGND       | Supply               | Digital negative supply                                                                   |

| 16  | CSB        | Digital input        | Serial interface Latch signal (5V tolerant)                                               |

| 17  | SCLK       | Digital input        | Serial interface clock (5V tolerant)                                                      |

| 18  | SDIN       | Digital input        | Serial interface data (5V tolerant)                                                       |

| 19  | AIN1L      | Analogue Input       | Channel 1 left input multiplexor virtual ground                                           |

| 20  | AIN1R      | Analogue Input       | Channel 1 right input multiplexor virtual ground                                          |

| 21  | AIN2L      | Analogue Input       | Channel 2 left input multiplexor virtual ground                                           |

| 22  | AIN2R      | Analogue Input       | Channel 2 right input multiplexor virtual ground                                          |

| 23  | AIN3L      | Analogue Input       | Channel 3 left input multiplexor virtual ground                                           |

| 24  | AIN3R      | Analogue Input       | Channel 3 right input multiplexor virtual ground                                          |

| 25  | AIN4L      | Analogue Input       | Channel 4 left input multiplexor virtual ground                                           |

| 26  | AIN4R      | Analogue Input       | Channel 4 right input multiplexor virtual ground                                          |

| 27  | AIN5L      | Analogue Input       | Channel 5 left input multiplexor virtual ground                                           |

| 28  | AIN5R      | Analogue Input       | Channel 5 right input multiplexor virtual ground                                          |

| 29  | AIN6L      | Analogue Input       | Channel 6 left input multiplexor virtual ground                                           |

| 30  | AIN6R      | Analogue Input       | Channel 6 right input multiplexor virtual ground                                          |

| 31  | AINOPL     | Analogue Output      | Left channel multiplexor output                                                           |

| 32  | AINVGL     | Analogue Input       | Left channel multiplexor virtual ground                                                   |

| 33  | AINVGR     | Analogue Input       | Right channel multiplexor virtual ground                                                  |

| 34  | AINOPR     | Analogue Output      | Right channel multiplexor output                                                          |

| 35  | RECL       | Analogue Output      | Left channel input mux select output                                                      |

| 36  | RECR       | Analogue Output      | Right channel input mux select output                                                     |

| 37  | AVDDADC    | Supply               | Analogue positive supply for ADC                                                          |

| 38  | REFADCP    | Analogue Output      | ADC reference buffer decoupling pin; 10uF external decoupling                             |

| 39  | VMIDADC    | Analogue Output      | ADC midrail divider decoupling pin; 10uF external decoupling                              |

| 40  | AGNDADC    | Supply               | Analogue negative supply and substrate connection for ADC                                 |

| 41  | REFADCN    | Supply               | ADC ground reference                                                                      |

| 42  | DACREFP1   | Supply               | DAC positive reference supply                                                             |

| 43  | DACREFN1   | Supply               | DAC ground reference                                                                      |

| 44  | VMIDDAC1   | Analogue output      | DAC midrail decoupling pin ; 10uF external decoupling                                     |

| 45  | RAUXSOP    | Analogue output      | Right aux/rear channel summer output                                                      |

| 46  | RAUXBMIN   | Analogue input       | Right Aux/rear channel bass managed filtered input                                        |

| 47  | LAUXSOP    | Analogue output      | Left aux/rear channel summer output                                                       |

| 48  | LAUXBMIN   | Analogue input       | Left Aux/rear channel bass managed filtered input                                         |

| 49  | AUXR       | Analogue output      | DAC aux or rear channel right output                                                      |

|     |            |                      |                                                                                           |

| PIN | NAME     | TYPE                 | DESCRIPTION                                                       |

|-----|----------|----------------------|-------------------------------------------------------------------|

| 51  | RRBMIN   | Analogue input       | Right surround channel bass managed filtered input                |

| 52  | RSURSOP  | Analogue output      | Right surround channel summer output                              |

| 53  | SURR     | Analogue output      | DAC surround channel right output                                 |

| 54  | LRBMIN   | Analogue input       | Left surround channel bass managed filtered input                 |

| 55  | LSURSOP  | Analogue output      | Left surround channel summer output                               |

| 56  | SURL     | Analogue output      | DAC surround channel left output                                  |

| 57  | AUX3R    | Analogue input       | 3.1 Multiplexor channel 3 right virtual ground input              |

| 58  | AUX3L    | Analogue input       | 3.1 Multiplexor channel 3 left virtual ground input               |

| 59  | LFE      | Analogue output      | DAC LFE channel right output                                      |

| 60  | LFEVE    | Analogue Input       | LFE channel summer virtual earth                                  |

| 61  | LFESUM   | Analogue output      | LFE channel summer output                                         |

| 62  | LFESOP   | Analogue output      | LFE channel summer output                                         |

| 63  | AVDDDAC  | Supply               | Analogue positive supply for DAC                                  |

| 64  | AGNDDAC  | Supply               | Analogue negative supply and substrate connection for DAC         |

| 65  | HPHONER  | Analogue output      | Headphone channel right output                                    |

| 66  | HPHONEL  | Analogue output      | headphone channel left output                                     |

| 67  | AUX2R    | Analogue input       | 3.1 Multiplexor channel 2 right virtual ground input              |

| 68  | AUX2L    | Analogue input       | 3.1 Multiplexor channel 2 left virtual ground input               |

| 69  | CNTR     | Analogue output      | DAC centre channel right output                                   |

| 70  | CNTSOP   | Analogue output      | Centre front channel summer output                                |

| 71  | CIN3     | Analogue input       | Centre channel bass management filter input                       |

| 72  | CIN2     | Analogue input       | Centre channel bass filter input                                  |

| 73  | CIN1     | Analogue input       | Centre channel treble filter input                                |

| 74  | FRONTR   | Analogue output      | DAC front channel right output                                    |

| 75  | RIN3     | Analogue input       | Right front channel bass management filter input                  |

| 76  | RIN2     | Analogue input       | Right front channel bass filter input                             |

| 77  | RIN1     | Analogue input       | Right front channel treble filter input                           |

| 78  | RSUMOP   | Analogue output      | Right front channel summer output                                 |

| 79  | FRONTL   | Analogue output      | DAC front channel left output                                     |

| 80  | LIN3     | Analogue input       | Left front channel bass management filter input                   |

| 81  | LIN2     | Analogue input       | Left front channel bass filter input                              |

| 82  | LIN1     | Analogue input       | Left front channel treble filter input                            |

| 83  | LSUMOP   | Analogue output      | Left front channel summer output                                  |

| 84  | AUX1R    | Analogue input       | 3.1 Multiplexor channel 1 right virtual ground input              |

| 85  | AUX1L    | Analogue input       | 3.1 Multiplexor channel 1 left virtual ground input               |

| 86  | VMIDDAC2 | Analogue output      | DAC midrail decoupling pin ; 10uF external decoupling             |

| 87  | DACREFN2 | Supply               | DAC ground reference                                              |

| 88  | DACREFP2 | Supply               | DAC positive reference supply                                     |

| 89  | GPIO1    | Digital input/output | Selectable i/o (S/PDIF input, status flag output or ADCMCLK)      |

| 90  | GPIO2    | Digital input/output | Selectable i/o (S/PDIF input, status flag output, or PDATAOPBCLK) |

| 91  | GPIO3    | Digital input/output | Selectable i/o (S/PDIF input or status flag output)               |

| 92  | GPO/MODE | Digital input/output | Selectable i/o (state at RESET determines control interface type) |

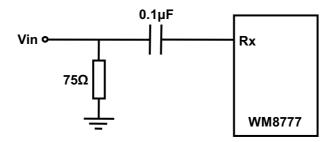

| 93  | SPIN     | Digital input        | S/PDIF input                                                      |

| 94  | SPDIFOP  | Digital output       | S/PDIF output                                                     |

| 95  | SPBCLK   | Digital input/output | Secondary Audio Interface bit clock                               |

| 96  | SLRC     | Digital input/output | Secondary Audio Interface left/right clock                        |

| 97  | SDATAOP  | Digital output       | Secondary Audio Interface output data                             |

| 98  | SDATAIP  | Digital Input        | Secondary Audio Interface input data                              |

| 99  | ХТО      | Crystal op           | Crystal oscillator output                                         |

| 100 | XTI      | Digital input        | Crystal oscillator or external clock inputs                       |

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

As per specification IPC/JEDEC J-STD-020B, this product requires specific storage conditions prior to surface mount assembly. It has a Moisture Sensitivity Level of 3 and as such will be supplied in vacuum-sealed moisture barrier bags, with an out of bag exposure time limit of 1 week at less than 30°C / 60% RH.

| CONDITION                                                                       | MIN        | МАХ         |

|---------------------------------------------------------------------------------|------------|-------------|

| Digital supply voltage                                                          | -0.3V      | +3.63V      |

| Analogue supply voltage                                                         | -0.3V      | +7V         |

| Voltage range digital inputs (SDIN, SCLK, CSB)                                  | DGND -0.3V | +7V         |

| Voltage range digital inputs (MCLK, DIN[3:0], PDATAOPLRC, PDATAIPLRC and PBCLK) | DGND -0.3V | DVDD + 0.3V |

| Voltage range analogue inputs                                                   | AGND -0.3V | AVDD +0.3V  |

| Master Clock Frequency                                                          |            | 37MHz       |

| Operating temperature range, T <sub>A</sub>                                     | -25°C      | +85°C       |

| Storage temperature                                                             | -65°C      | +150°C      |

Note:

1. Analogue and digital grounds must always be within 0.3V of each other.

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                        | SYMBOL                                    | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|--------------------------------------------------|-------------------------------------------|-----------------|------|-----|------|------|

| Digital supply range                             | DVDD                                      |                 | 2.7  |     | 3.6  | V    |

| Analogue supply range                            | AVDDDAC,AVDDACD,                          |                 | 4.5  |     | 5.5  | V    |

|                                                  | PVDD                                      |                 |      |     |      |      |

| Analogue Reference range                         | VREFP                                     |                 | 4.5  |     | 5.5  |      |

| Ground                                           | AGNDDAC,<br>AGNDADC, PGND,<br>DGND, VREFN |                 |      | 0   |      | V    |

| Difference DGND to<br>AGNDDAC/AGNDADC/PLL<br>GND |                                           |                 | -0.3 | 0   | +0.3 | V    |

# ELECTRICAL CHARACTERISTICS

#### **Test Conditions**

AVDDDAC = 5V, AVDDADC=5V, DVDD = 3.3V, AGNDDAC = 0V, AGNDADC = 0, DGND = 0V, T<sub>A</sub> =  $+25^{\circ}$ C, fs = 48kHz, MCLK = 256fs, ADC/DAC in Slave Mode unless otherwise stated.

| PARAMETER                             | SYMBOL                  | TEST CONDITIONS                           | MIN         | TYP                | MAX        | UNIT |

|---------------------------------------|-------------------------|-------------------------------------------|-------------|--------------------|------------|------|

| Digital Logic Levels ( CMOS Lev       | els)                    |                                           |             |                    | . I        |      |

| Input LOW level                       | VIL                     |                                           |             |                    | 0.3 X DVDD | V    |

| Input HIGH level                      | VIH                     |                                           | 0.7 X DVDD  |                    |            | V    |

| Input Leakage Current                 |                         |                                           |             | ±0.2               |            | μA   |

| Input Capacitance                     |                         |                                           |             | 5                  |            | pF   |

| Output LOW                            | V <sub>OL</sub>         | I <sub>OL</sub> =1mA                      |             |                    | 0.1 x DVDD | V    |

| Output HIGH                           | VoH                     | I <sub>OH</sub> -1mA                      | 0.9 x DVDD  |                    |            | V    |

| Analogue Reference Levels             |                         |                                           |             | 1                  | 11         |      |

| Reference voltage                     | V <sub>VMID (DAC)</sub> |                                           |             | VREFP/2            |            | V    |

|                                       | V <sub>VMID</sub> (ADC) |                                           |             | AVDDADC/2          |            | V    |

| Potential divider resistance          | RVMID (DAC)             | VREFP to VMID and<br>VMID to VREFN        |             | 50k                |            | Ω    |

|                                       | R <sub>VMID (ADC)</sub> | AVDDADC to VMID<br>and VMID to<br>AGNDADC |             | 50k                |            | Ω    |

| DAC Performance (Load = 10k Ω         | , 50pF) to pins         | L/RSUMOP, CNTSOP,                         | LFESOP, L/F | SUROP, L/RA        | UXSOP      |      |

| 0dBFs Full scale output voltage       |                         |                                           |             | 1.0 x              |            | Vrms |

| · -                                   |                         |                                           |             | VREFP/5            |            |      |

| SNR (Note 1,2)                        |                         | A-weighted,<br>@ fs = 48kHz               | 100         | 108                |            | dB   |

| SNR (Note 1,2)                        |                         | A-weighted<br>@ fs = 96kHz                |             | 108                |            | dB   |

| Dynamic Range (Note 2)                | DNR                     | A-weighted, -60dB<br>full scale input     | 100         | 108                |            | dB   |

| Total Harmonic Distortion (THD)       |                         | 1kHz, 0dBFs                               |             | -94                | -90        | dB   |

| DAC channel separation                |                         |                                           |             | 110                |            | dB   |

| DAC Mute attenuation                  |                         | 1KHz Input, 0dB gain                      |             | 100                |            | dB   |

| Power Supply Rejection Ratio          | PSRR                    | 1kHz 100mVpp                              |             | 50                 |            | dB   |

|                                       |                         | 20Hz to 20kHz<br>100mVpp                  |             | 45                 |            | dB   |

| DAC Digital Volume                    |                         |                                           |             |                    |            |      |

| DAC Digital volume control<br>range   |                         |                                           | -127.5      |                    | 0          | dB   |

| DAC Digital volume step size          |                         |                                           |             | 0.5                |            | dB   |

| ADC Performance                       |                         |                                           |             |                    |            |      |

| Input Signal Level (0dB)              |                         |                                           |             | 1.0 x<br>AVDDADC/5 |            | Vrms |

| SNR (Note 1,2)                        |                         | A-weighted, 0dB gain<br>@ fs = 48kHz      | 93          | 102                |            | dB   |

| SNR (Note 1,2)                        |                         | A-weighted, 0dB gain<br>@ fs = 96kHz      |             | 100                |            | dB   |

| Dynamic Range (note 2)                |                         | A-weighted, -60dB<br>full scale input     |             | 102                |            | dB   |

| Total Harmonic Distortion (THD)       |                         | 1kHz, 0dBFs                               |             | -89                | Τ          | dB   |

|                                       |                         | 1kHz, -1dBFs                              |             | -94                | -85        | dB   |

| ADC Channel Separation                |                         | 1kHz Input                                |             | 85                 |            | dB   |

| Programmable Gain Step Size           |                         |                                           |             | 0.5                |            | dB   |

| Programmable Gain Range<br>(Analogue) |                         | 1kHz Input                                | -21         |                    | +24        | dB   |

| Programmable Gain Range<br>(Digital)  |                         | 1kHz Input                                | -103        |                    | -21.5      | dB   |

| Mute Attenuation                      |                         | 1kHz Input, 0dB gain                      |             | 82                 |            | dB   |

| Power Supply Rejection Ratio          | PSRR                    | 1kHz 100mVpp                              |             | 50                 |            | dB   |

#### **Test Conditions**

AVDDDAC = 5V, AVDDADC=5V, DVDD = 3.3V, AGNDDAC = 0V, AGNDADC = 0, DGND = 0V, T<sub>A</sub> = +25°C, fs = 48kHz, MCLK = 256fs, ADC/DAC in Slave Mode unless otherwise stated.

| PARAMETER                                                | SYMBOL        | TEST CONDITIONS          | MIN         | TYP                | MAX        | UNIT      |

|----------------------------------------------------------|---------------|--------------------------|-------------|--------------------|------------|-----------|

|                                                          |               | 20Hz to 20kHz<br>100mVpp |             | 45                 |            | dB        |

| Input Resistance (AIN1 -> AIN6)                          |               |                          |             | 20                 |            | kΩ        |

| Input Capacitance<br>(AIN1 -> AIN6)                      |               |                          |             | 10                 |            | pF        |

| ADC PGA Output to Analogue Ou<br>gain = 0dB) Bypass Mode | utput (L/RSUN | IOP, CNTSOP, LFESOP,     | L/RSURO     | P, L/RAUXSOP) (    | Load=10k 0 | 2, 50pF,  |

| 0dB Full scale output voltage                            |               |                          |             | 1.0 x              |            | Vrms      |

|                                                          |               |                          |             | AVDDDAC/5          |            |           |

| SNR (Note 1)                                             |               |                          | 90          | 104                |            | dB        |

| THD                                                      |               | 1kHz, 0dB                |             | -93                |            | dB        |

|                                                          |               | 1kHz, -3dB               |             | -95                |            | dB        |

| Power Supply Rejection Ratio                             | PSRR          | 1kHz 100mVpp             |             | 50                 |            | dB        |

|                                                          |               | 20Hz to 20kHz 100mV      |             | 45                 |            | dB        |

| Mute Attenuation                                         |               | 1kHz, 0dB                |             | 100                |            | dB        |

| Analogue Input (AIN6) to Analog                          | ue Output (FR | ONTL, FRONTR) (Load=     | =10k Ω, 50p | F, gain = 0dB) B   | ypass Mode | 9         |

| 0dB Full scale output voltage                            |               |                          | -           | 1.0 x<br>AVDDDAC/5 |            | Vrms      |

| SNR (Note 1)                                             |               |                          | 90          | 104                |            | dB        |

| ( )                                                      |               |                          | 90          | -                  |            | -         |

| THD                                                      |               | 1kHz, 0dB                |             | -93                |            | dB        |

|                                                          | 5055          | 1kHz, -3dB               |             | -95                |            | dB        |

| Power Supply Rejection Ratio                             | PSRR          | 1kHz 100mVpp             |             | 50                 |            | dB        |

|                                                          |               | 20Hz to 20kHz 100mV      |             | 45                 |            | dB        |

| Mute Attenuation                                         |               | 1kHz, 0dB                |             | 100                |            | dB        |

| ADC PGA to REC Output                                    |               |                          |             |                    |            | r         |

| 0dB Full scale output voltage                            |               |                          |             | 1.0 x<br>AVDDDAC/5 |            | Vrms      |

| SNR (Note 1)                                             |               |                          | 90          | 104                |            | dB        |

| THD                                                      |               | 1kHz, 0dB                |             | -93                |            | dB        |

|                                                          |               | 1kHz, -3dB               |             | -95                |            | dB        |

| Power Supply Rejection Ratio                             | PSRR          | 1kHz 100mVpp             |             | 50                 |            | dB        |

|                                                          |               | 20Hz to 20kHz 100mV      |             | 45                 |            | dB        |

| Mute Attenuation                                         |               | 1kHz, 0dB                |             | 100                |            | dB        |

|                                                          |               | TKTIZ, OUD               |             | 100                |            | uD        |

| L/RSUMOP to REC Output                                   |               | 1                        |             | 1.0                |            | ) (maging |

| 0dB Full scale output voltage                            |               |                          |             | 1.0 x              |            | Vrms      |

|                                                          |               |                          | ~~~         | AVDDDAC/5          |            |           |

| SNR (Note 1)                                             |               |                          | 90          | 104                |            | dB        |

| THD                                                      |               | 1kHz, 0dB                |             | -93                |            | dB        |

|                                                          |               | 1kHz, -3dB               |             | -95                |            | dB        |

| Power Supply Rejection Ratio                             | PSRR          | 1kHz 100mVpp             |             | 50                 |            | dB        |

|                                                          |               | 20Hz to 20kHz 100mV      |             | 45                 |            | dB        |

| Mute Attenuation                                         |               | 1kHz, 0dB                |             | 100                |            | dB        |

| Volume Controls (FRONTL, FRO                             | NTR, CNTR, L  | FE, SURR, SURL, AUXL     | , AUXR, HP  | HONER, HPHON       | IEL, LFESU | M)        |

| Analogue output Volume Gain<br>Step Size                 |               |                          | 0.5         | 1                  | 1.5        | dB        |

| Analogue output Volume Gain<br>Range                     |               | 1kHz Input               | -100        |                    | +20        | dB        |

| Analogue output Volume Mute<br>Attenuation               |               | 1kHz Input, 0dB gain     |             | 100                |            | dB        |

| Analogue Tone volume step size                           |               | 1                        |             | 1                  |            | dB        |

Product Preview

#### **Test Conditions**

AVDDDAC = 5V, AVDDADC=5V, DVDD = 3.3V, AGNDDAC = 0V, AGNDADC = 0, DGND = 0V,  $T_A$  = +25°C, fs = 48kHz, MCLK = 256fs, ADC/DAC in Slave Mode unless otherwise stated.

| PARAMETER                                     | SYMBOL             | TEST CONDITIONS      | MIN        | TYP  | MAX        | UNIT    |

|-----------------------------------------------|--------------------|----------------------|------------|------|------------|---------|

| Analogue Bass Management an                   | d Tone Control     | s                    |            |      |            |         |

| Treble range adjustment                       |                    |                      | -10        |      | +10        | dB      |

| Treble step size                              |                    |                      |            | 1    |            | dB      |

| Bass range adjustment                         |                    |                      | -10        |      | +10        | dB      |

| Bass step size                                |                    |                      |            | 1    |            | dB      |

| Headphone Amplifier at 0dB Vo                 | lume (Load=16      | Ω, at 1Vrms)         |            |      |            |         |

| Headphone output level                        |                    |                      |            | 1.5  |            | Vrms    |

| THD                                           |                    |                      |            | -74  |            | dB      |

| SNR                                           |                    |                      |            | -96  |            | dB      |

| Headphone Amplifier at 0dB Vo                 | lume (Load=32      | Ω, at 1Vrms)         |            |      |            |         |

| Headphone output level                        |                    |                      |            | 0.95 |            | Vrms    |

| THD                                           |                    |                      |            | -68  |            | dB      |

| SNR                                           |                    |                      |            | -100 |            | dB      |

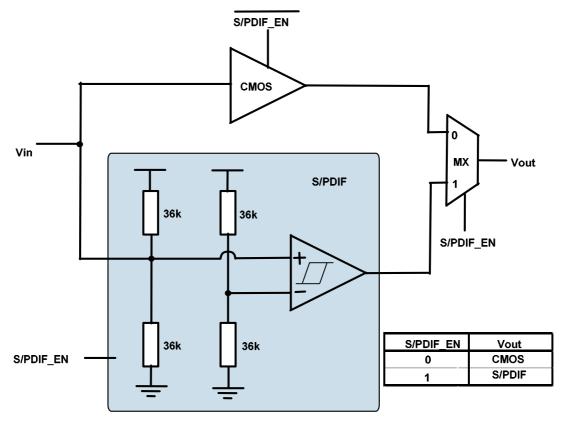

| S/PDIF Transceiver                            | •                  | ·                    |            |      |            |         |

| Jitter on recovered clock (Rms period jitter) |                    |                      |            | 50   |            | Ps      |

| S/PDIF Input Levels CMOS MODE                 | •                  |                      | 1 1        |      |            |         |

| Input LOW level                               | VIL                |                      |            |      | 0.3 X DVDD | V       |

| Input HIGH level                              | VIH                |                      | 0.7 X DVDD |      |            | V       |

| Input capacitance                             |                    |                      |            | 1.25 |            | pF      |

| Input Frequency                               |                    |                      |            |      | 36         | MHz     |

| S/PDIF Input Levels Comparato                 | r MODE             |                      |            |      |            |         |

| Input capacitance                             |                    |                      |            | 1.31 |            | pF      |

| Input resistance                              |                    |                      |            | 18   |            | Ω       |

| Input frequency                               |                    |                      |            |      | 25         | MHz     |

| Input Amplitude                               |                    |                      | 200        |      | 0.5 X DVDD | mV      |

| PLL                                           |                    |                      |            |      |            |         |

| Period Jiffer                                 |                    |                      |            | 80   |            | ps(rms) |

| XTAL                                          |                    |                      |            |      |            |         |

| Input XTI LOW level                           | VX <sub>IL</sub>   |                      | 0          |      | 557        | mV      |

| Input XTI HIGH level                          | VXI <sub>H</sub>   |                      | 853        |      |            | mV      |

| Input XTI capacitance                         | C <sub>XJ</sub>    |                      | 3.32       |      | 4.491      | pF      |

| Input XTI leakage                             | IX <sub>leak</sub> |                      | 28.92      |      | 38.96      | mA      |

| Output XTO LOW                                | VX <sub>OL</sub>   | 15pF load capacitors | 86         |      | 278        | mV      |

| Output XTO HIGH                               | VX <sub>OH</sub>   | 15pF load capacitors | 1.458      |      | 1.942      | V       |

Notes:

1. Ratio of output level with 1kHz full scale input, to the output level with all zeros into the digital input, measured 'A' weighted.

2. All performance measurements done with 20kHz low pass filter, and where noted an A-weight filter. Failure to use such a filter will result in higher THD+N and lower SNR and Dynamic Range readings than are found in the Electrical Characteristics. The low pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

3. VMID decoupled with 10uF and 0.1uF capacitors (smaller values may result in reduced performance).

### TERMINOLOGY

- 1. Signal-to-noise ratio (dB) SNR is a measure of the difference in level between the full scale output and the output with no signal applied. (No Auto-zero or Automute function is employed in achieving these results).

- Dynamic range (dB) DNR is a measure of the difference between the highest and lowest portions of a signal. Normally a THD+N measurement at 60dB below full scale. The measured signal is then corrected by adding the 60dB to it. (e.g. THD+N @ -60dB= -32dB, DR= 92dB).

- 3. THD+N (dB) THD+N is a ratio, of the rms values, of (Noise + Distortion)/Signal.

- 4. Stop band attenuation (dB) Is the degree to which the frequency spectrum is attenuated (outside audio band).

- 5. Channel Separation (dB) Also known as Cross-Talk. This is a measure of the amount one channel is isolated from the other. Normally measured by sending a full scale signal down one channel and measuring the other.

- 6. Pass-Band Ripple Any variation of the frequency response in the pass-band region.

# SUPPLY CURRENT

The supply current of the WM877 depends on the operating mode. For example, the supply current is lower when the device is used for playback-only (ADC off) or recording-only (DACs off). The supply currents for various operating modes are shown in Table 1 below.

| MODE DESCRIPTION                                      |         | SU      | PPLY CU | RRENT |        |      |

|-------------------------------------------------------|---------|---------|---------|-------|--------|------|

|                                                       | AVDDDAC | AVDDADC | PVDD    | DVDD  | TOTAL  | UNIT |

| On power-up, no clks applied                          | 2.81    | 1.89    | 0.30    | 0.39  | 5.39   | mA   |

| On power-up, clks applied                             | 2.81    | 1.89    | 0.30    | 1.70  | 6.70   | mA   |

| ADC                                                   | 2.71    | 38.86   | 0.30    | 5.80  | 47.67  | mA   |

| All DACs                                              | 55.35   | 1.90    | 0.30    | 18.61 | 76.16  | mA   |

| ADC, All DACs                                         | 53.45   | 38.69   | 0.30    | 22.4  | 114.84 | mA   |

| ADC, All DACs, Osc                                    | 53.44   | 38.70   | 1.12    | 22.4  | 115.66 | mA   |

| ADC, All DACs, Osc, PLL                               | 53.38   | 38.62   | 3.74    | 28.65 | 124.39 | mA   |

| ADC, All DACs, Osc, PLL, S/PDIF                       | 53.38   | 38.62   | 3.43    | 29.89 | 125.32 | mA   |

| ADC, All DACs, Osc, PLL, S/PDIF, Tone                 | 87.53   | 38.53   | 3.43    | 29.99 | 159.48 | mA   |

| ADC, All DACs, Osc, PLL, S/PDIF, Tone,<br>HP (16 Ohm) | 146.60  | 38.42   | 3.44    | 29.99 | 218.45 | mA   |

| Power-down, no clks applied                           | 0.028   | 0.172   | 0.30    | 0.39  | 0.89   | mA   |

| Power-down, clks applied                              | 0.028   | 0.172   | 0.30    | 1.60  | 2.10   | mA   |

| Software RESET                                        | 2.80    | 1.88    | 0.3     | 0.95  | 5.93   | mA   |

Table 1 Supply Current for Functional Blocks

Notes:

- 1. DAC Analogue supply (AVDDDAC) = 5V.

- 2. ADC Analogue supply (AVDDADC) = 5V.

- 3. PLL Analogue supply (PVDD) = 5V.

- 4. Digital supply (DVDD) = 3.3V.

#### **DEVICE DESCRIPTION**

#### INTRODUCTION

WM8777 is a complete 8-channel DAC, 2-channel ADC audio codec, with integrated S/PDIF transceiver, analogue tone controls and bass management including analogue volume controls on each channel.

The device is implemented as four separate stereo DACs and a stereo ADC with flexible input multiplexer, in a single package and controlled by a single interface.

The four stereo channels may either be used to implement a 5.1 channel surround system, with additional stereo channel for a stereo mix down channel, or for a complete 7.1 channel surround system.

An analogue bypass path option is available, to allow stereo analogue signals from any of the 8 stereo inputs to be sent to the stereo outputs via the main volume controls. This allows a purely analogue input to analogue output high quality signal path to be implemented if required. This would allow, for example, the user to play back a 5.1 channel surround movie through 6 of the DACs, whilst playing back a separate analogue or digital signal into a remote room installation.

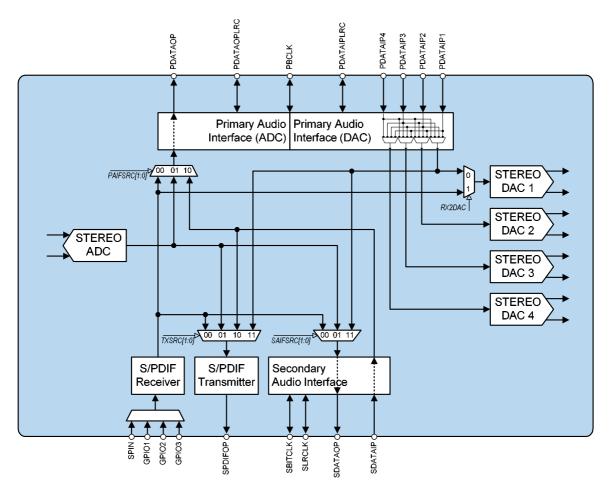

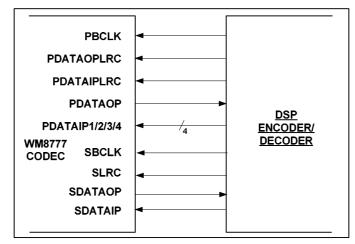

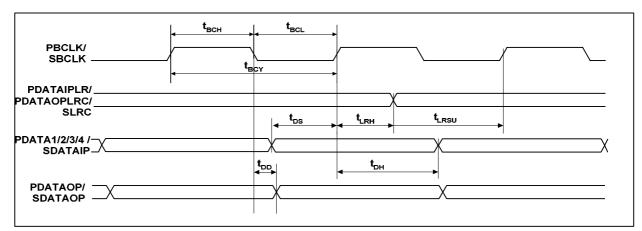

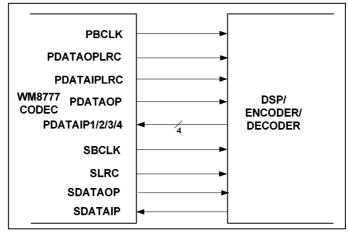

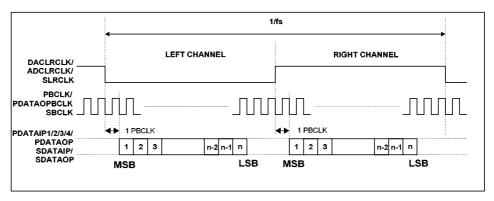

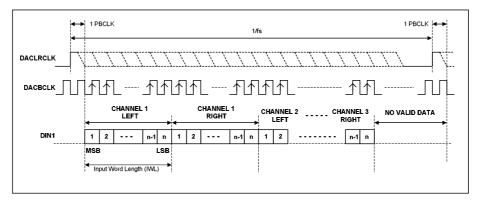

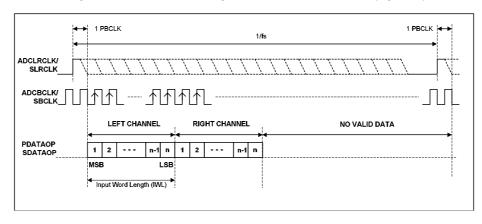

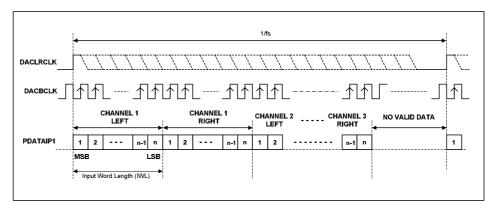

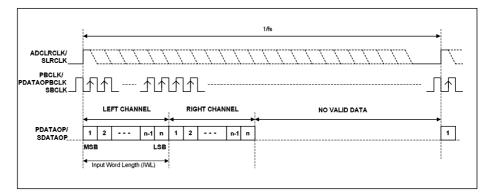

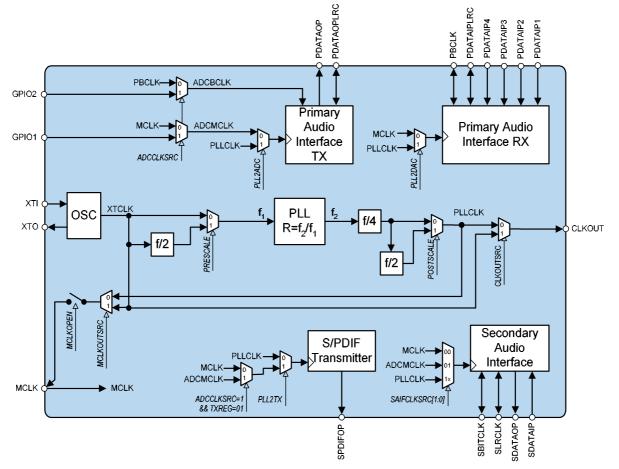

The WM8777 has two digital audio interfaces. The primary audio interface has separate inputs for each stereo DAC, and one data output which can output digital data from the ADC, received S/PDIF data or data received from the secondary audio interface. Data directed to DAC1 is also directed to the S/PDIF transmitter. The secondary audio interface has a single data input and a single data output. The input data can be output over the primary audio interfaces, or converted into S/PDIF format and output over the S/PDIF transmitter. Both audio interfaces may be configured to operate in either master or slave mode and support right justified, left justified and I<sup>2</sup>S interface formats along with a highly flexible DSP serial port interface.

The input multiplexor to the ADC is configured to allow large signal levels to be input to the ADC, using external resistors to reduce the amplitude of larger signals to within the normal operating range of the ADC. The ADC input PGA also allows input signals to be gained up to +24dB and attenuated down to -21dB. This allows the user maximum flexibility in the use of the ADC.

A selectable stereo record output is also provided on RECL/R. It is intended that the RECL/R outputs are only used to drive a high impedance buffer.

Each DAC has its own digital volume control. The digital volume control changes can be made in 0.5dB steps. In addition a zero cross detect circuit is provided for each DAC. The digital volume control detects a transition through the zero point before updating the volume. This minimises audible clicks and 'zipper' noise as the gain values change. In addition to this there is an analogue volume control on each of the tone outputs, with a zero cross detect circuit. The analogue volume control changes can be made in 1dB steps. When analogue volume zero-cross detection is enabled the attenuation values are only updated when the input signal to the gain stage is close to the analogue ground level.

Additionally, 6 of the DAC outputs incorporate an input selector and mixer allowing an external 6 channel, or 5.1 channel signal, to be either switched into the signal path in place of the DAC signal or mixed with the DAC signal.

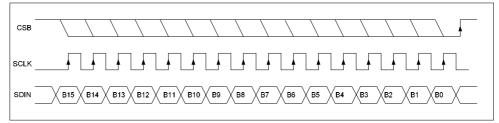

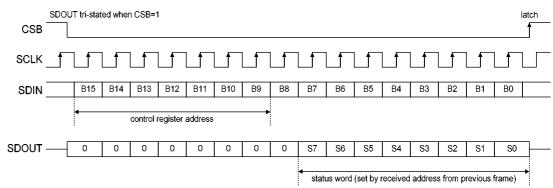

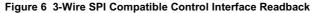

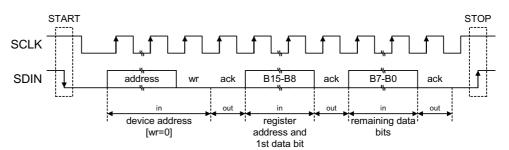

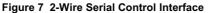

Control of internal functionality of the device is by 3-wire SPI or 2-wire serial control interface selectable by the state of the GPO/MODE pin on power up. The control interface may be asynchronous to the audio data interface as control data will be re-synchronised to the audio processing internally.

CSB, SCLK, and SDIN are 5V tolerant with TTL input thresholds, allowing the WM8777 to be used with DVDD = 3.3V and be controlled by a controller with 5V output.

Operation using a system clock of 128fs, 192fs, 256fs, 384fs, 512fs, 768fs or 1152fs is provided. In Slave mode selection between clock rates is automatically controlled. In master mode the master clock to sample rate ratio is set by control bits PAIFTX\_RATE and PAIFRX\_RATE. The ADC and DAC may run at different rates within the constraint of a common master clock. For example with master clock at 24.576MHz, a DAC sample rate of 96kHz (256fs mode) and an ADC sample rate of 48kHz (512fs mode) can be accommodated. Sample rates (fs) from less than 8ks/s up to 192ks/s are allowed, provided the appropriate system clock is input.

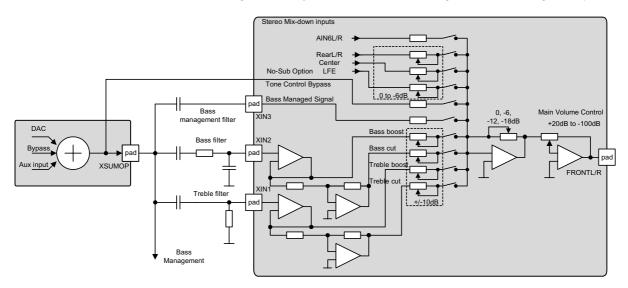

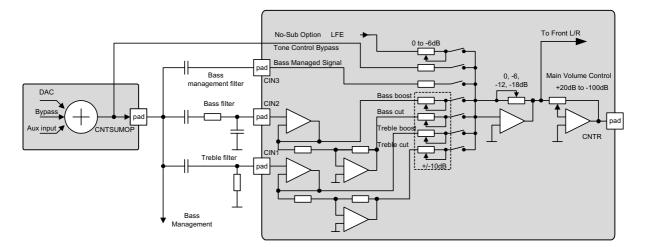

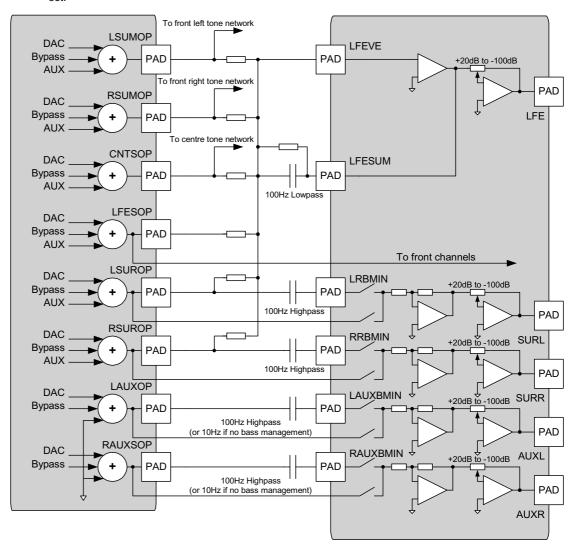

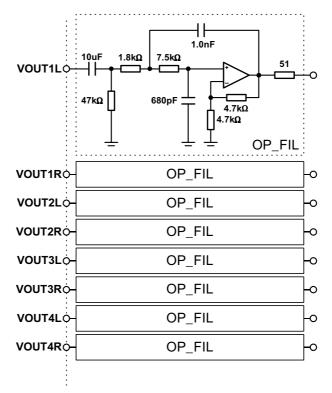

#### ANALOGUE TONE CONTROLS

Facilities are provided for implementation of analogue treble and bass tone controls on each of the Front left, right and centre channels. External R and C values are used to set the corner frequencies of these tone control functions, allowing the system builder to choose the required responses.

Adjustment of the amplitude of the required tone response is made electronically by writing the required gain or attenuation value into the WM8777 over the serial control interface. Maximum boost or attenuation of tone control values of +/-10dB in 1dB steps is provided.

A tone control bypass path is provided, plus input summing paths for Rear (i.e. Surround L/R), Centre and LFE channels, to allow for creation of a stereo 'mix-down' signal when only two speakers are supported. Each of these mix-down paths has independent gain adjust from 0dB to -6db in 1dB steps.

An analogue input bypass path is also provided. This allows AIN6L and AIN6R to be output on the FRONTL and FRONTR output channels making use of the volume controls if required.

In order to provide sufficient headroom for cases where significant amounts of analogue treble or bass boost have been applied, a gain attenuation control is provided in the summing stage after the tone adjust PGAs. This allows attenuation of -6dB, -12dB or -18dB to be applied. Re-adjustment of the nominal 0dB signal level may then be made in the following volume control stage as required.

Figure 1 Tone Control Configuration - Front Left/Right (single channel shown)

Figure 2 Tone Control Configuration - Centre Channel

#### MIXER CONTROL

Control of the front channel signal paths is via five software registers. The first three registers control both the front left and right channels whilst the remaining two control the centre channel. When only two speakers are available a stereo mix-down signal can be created by setting the REAR, CNTR and LFE bits of the appropriate register.

Control of the tone characteristics for a channel is determined by writing to the XTRBL and XBASS register bits (where X implies either Front L/R or Centre channel). The tone controls work by adding/subtracting high/low-pass filtered signal content to the nominal 0dB bass-managed signal. Thus when using the tone controls, the XBM bit should also be set. Note also that cut and boost cannot be applied simultaneously. If both bits are set, the tone control signal path will be bypassed but the amplifiers will remain enabled. To avoid pop-noises during dynamic tone control it is recommending that this method is used to disable the tone control signal path. Setting both bits low disables the path, however it will also cause the amplifiers to power down.

The mixer control registers (FTRBL, FBASS, CTRBL and CBASS) share the zero-cross detect circuit used by the analogue volume control. Thus the ZCEN enable bit for a particular channel can be used to determine whether or not the tone control signal path select signals are updated only on a zero-cross condition.

The bypass path is selected by setting the FBYP bit for the front L/R channels and the CBYP bit for the centre channel. The centre, rear and LFE channels can all be independently summed into the front L/R channels by setting the CNTR, REAR and FLFE bits respectively. Each of these signal paths has independent gain control from 0 to -6dB, adjustable in 1dB steps. These gains are determined by writing to the attenuation registers CNTRGAIN, REARGAIN and FLFEGAIN respectively.

The LFE channel can also be summed into the front centre channel by setting the CLFE bit. This path also has independent gain control from 0 to -6dB, controlled by writing to the CLFEGAIN register.

| REGISTER<br>ADDRESS      | BIT | LABEL         | DEFAULT | DESCRIPTION                        |

|--------------------------|-----|---------------|---------|------------------------------------|

| (22h)                    | 1:0 | FTRBL[1:0]    | 00      | Control treble boost and cut:-     |

| FRONT Mixer              |     |               |         | 00 = both off ( Amps disabled)     |

| Control 1                |     |               |         | 01 = Treble cut                    |

|                          |     |               |         | 10 = Treble boosted                |

|                          |     |               |         | 11 = both off (Amps enabled)       |

|                          | 3:2 | FBASS[1:0]    | 00      | Controls bass boost and cut:-      |

|                          |     |               |         | 00 = both off (Amps disabled)      |

|                          |     |               |         | 01 = Bass cut                      |

|                          |     |               |         | 10 = Bass boosted                  |

|                          |     |               |         | 11 = both off (Amps enabled)       |

|                          | 4   | FBM           | 0       | Bass Managed Signal path<br>select |

|                          |     |               |         | 0 = Open                           |

|                          |     |               |         | 1 = Closed                         |

|                          | 5   | FBYP          | 0       | Tone Control Bypass signal         |

|                          |     |               |         | path select                        |

|                          |     |               |         | 0 = Open                           |

|                          |     |               |         | 1 = Closed                         |

|                          | 6   | AIN6          | 0       | 0 = AIN6 not selected              |

|                          |     |               |         | 1 = AIN6 applied to FRONT          |

|                          |     |               |         | channels                           |

| (23h)                    | 2:0 | FLFEGAIN[2:0] | 000     | Front LFE gain:                    |

| FRONT Mixer<br>Control 2 |     |               |         | 000 = 0dB                          |

| Control 2                |     |               |         | 001 = 1dB                          |

|                          |     |               |         | 010 = 2dB                          |

|                          |     |               |         | 011 = 3dB                          |

|                          |     |               |         | 100 = 4dB                          |

|                          |     |               |         | 101 = 4.5dB                        |

|                          |     |               |         | 110 = 5dB                          |

|                          |     |               |         | 111 = 6dB                          |

|                          |     |               |         |                                    |

|                          |     |               |         |                                    |

PP Rev 1.94 November 2004

| REGISTER<br>ADDRESS       | BIT | LABEL         | DEFAULT | DESCRIPTION                   |

|---------------------------|-----|---------------|---------|-------------------------------|

|                           | 3   | FLFE          | 0       | LFE signal path select        |

|                           |     |               |         | 0 = Open                      |

|                           |     |               |         | 1 = Closed                    |

|                           | 6:4 | CNTRGAIN[2:0] | 000     | Front CNTR gain:              |

|                           |     |               |         | 000 = 0dB                     |

|                           |     |               |         | 001 = 1dB                     |

|                           |     |               |         | 010 = 2dB                     |

|                           |     |               |         | 011 = 3dB                     |

|                           |     |               |         | 100 = 4dB                     |

|                           |     |               |         | 101 = 4.5dB                   |

|                           |     |               |         | 110 = 5dB                     |

|                           |     |               |         | 111 = 6dB                     |

|                           | 7   | CNTR          | 0       | Centre signal path mix        |

|                           |     |               |         | 0 = Open                      |

|                           |     |               |         | 1 = Closed                    |

| (24h)                     | 2:0 | REARGAIN[2:0] | 000     | Front REAR gain:              |

| FRONT Mixer               |     |               |         | 000 = 0dB                     |

| Control 3                 |     |               |         | 001 = 1dB                     |

|                           |     |               |         | 010 = 2dB                     |

|                           |     |               |         | 011 = 3dB                     |

|                           |     |               |         | 100 = 4dB                     |

|                           |     |               |         | 101 = 4.5dB                   |

|                           |     |               |         | 110 = 5dB                     |

|                           |     |               |         | 111 = 6dB                     |

|                           | 3   | REAR          | 0       | Rear signal path mix          |

| (25h)                     | 1:0 | CTRBL[1:0]    | 00      | Control treble boost and cut: |

| Center Mixer              |     |               |         | 00 = both off                 |

| Control 1                 |     |               |         | 01 = Treble cut               |

|                           |     |               |         | 10 = Treble boosted           |

|                           |     |               |         | 11 = both off                 |

|                           | 3:2 | CBASS[1:0]    | 00      | Controls bass boost and cut:- |

|                           |     |               |         | 00 = both off                 |

|                           |     |               |         | 01 = Bass cut                 |

|                           |     |               |         | 10 = Bass boosted             |

|                           |     |               |         | 11 = both off                 |

|                           | 4   | CBM           | 0       | Bass Managed Signal path      |

|                           |     |               |         | select                        |

|                           |     |               |         | 0 = Open                      |

|                           |     |               |         | 1 = Closed                    |

|                           | 5   | CBYP          | 0       | Tone Control Bypass signal    |

|                           |     |               |         | path select                   |

|                           |     |               |         | 0 = Open                      |

| (00)                      |     |               |         | 1 = Closed                    |

| (26h)                     | 2:0 | CLFEGAIN[2:0] | 000     | Center LFE gain:-             |

| Center Mixer<br>Control 2 |     |               |         | 000 = 0dB                     |

| Control 2                 |     |               |         | 001 = 1dB                     |

|                           |     |               |         | 010 = 2dB                     |

|                           |     |               |         | 011 = 3dB                     |

|                           |     |               |         | 100 = 4 dB                    |

|                           |     |               |         | 101 = 4.5dB                   |

|                           |     |               |         | 110 = 5dB                     |

|                           | -   |               |         | 111 = 6dB                     |

|                           | 3   | CLFE          | 0       | LFE signal path select        |

|                           |     |               |         | 0 = Open                      |

|                           |     |               |         | 1 = Closed                    |

Table 2 Output Mixer Control Registers

#### TONE CONTROL GAIN

The amplitude of the tone response is controlled by writing gain values to the appropriate gain registers. The front left and right channels share gain registers, whilst the centre channel may be controlled independently. Table 3 shows how the attenuation levels for the tone control blocks are selected from the 4-bit code words.

The tone control attenuation registers share the zero-cross detect circuit used by the analogue volume control. Thus the ZCEN enable bit for a particular channel can be used to determine whether or not the treble/bass attenuation registers for that channel are updated only on a zero-cross condition.

| CUT/BOOST | CODE[3:0] | ATTENUATION LEVEL |

|-----------|-----------|-------------------|

|           | 0000      | +1dB              |

|           | 0001      | +2dB              |

| BOOST     |           |                   |

|           |           | -                 |

|           | 1001      | +10dB             |

| CUT       | 0000      | -1dB              |

|           | 0001      | -2dB              |

|           |           |                   |

|           |           |                   |

|           | 1001      | -10dB             |

Table 3 Tone Control Attenuation Levels

| REGISTER ADDRESS      | BIT | LABEL      | DEFAULT     | DESCRIPTION                                                                                                                                                                                                                |

|-----------------------|-----|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (28h)                 | 3:0 | FBASS[3:0] | 0000        | Gain control for Bass boost/cut                                                                                                                                                                                            |

| Front Bass Control    | 8   | UPDATE     | Not latched | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store GAIN FRONT BASS in<br>intermediate latch (no change to<br>output)<br>1 = Store GAIN FRONT BASS<br>and update attenuation on all<br>channels.       |

| (29h)                 | 3:0 | FTREB[3:0] | 0000        | Gain control for Bass boost/cut                                                                                                                                                                                            |

| Front Treble Control  | 8   | UPDATE     | Not latched | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store GAIN FRONT TREBLE<br>in intermediate latch (no change to<br>output)<br>1 = Store GAIN FRONT TREBLE<br>and update attenuation on all<br>channels.   |

| (2Ah)                 | 3:0 | CBASS[3:0] | 0000        | Gain control for Bass boost/cut                                                                                                                                                                                            |

| Center Bass Control   | 8   | UPDATE     | Not latched | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store GAIN CENTER BASS in<br>intermediate latch (no change to<br>output)<br>1 = Store GAIN CENTER BASS<br>and update attenuation on all<br>channels.     |

| (2Bh)                 | 3:0 | CTREB[3:0] | 0000        | Gain control for Bass boost/cut                                                                                                                                                                                            |

| Center Treble Control | 8   | UPDATE     | Not latched | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store GAIN CENTER TREBLE<br>in intermediate latch (no change to<br>output)<br>1 = Store GAIN CENTER TREBLE<br>and update attenuation on all<br>channels. |

Table 4 Tone Control Gain Registers

#### TONE CONTROL PRE-GAIN

The tone pre-gain is applied directly before the analogue volume control for a channel. This is to allow scaling of the channel response prior to the overall channel volume control.

Each of the front right, left and centre channels accept their own 2-bit gain code to determine to amount of attenuation applied. The Attenuation levels are given in Table 5.

| PRE-GAIN[0:1] | ATTENUATION |

|---------------|-------------|

| 00            | 0dB         |

| 01            | -6dB        |

| 10            | -12dB       |

| 11            | -18dB       |

Table 5 Tone Control Pre-Gain Attenuation

| REGISTER ADDRESS       | BIT | LABEL     | DEFAULT | DESCRIPTION                                                                                                                                                                                                      |

|------------------------|-----|-----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (2Ch)<br>Mixer Pregain | 1:0 | CNTP[1:0] | 00      | PREGAIN control for CNTR<br>control channel<br>00 = 0dB Attenuation<br>01 = -6dB Attenuation<br>10 = -12dB Attenuation<br>11 = -18dB Attenuation                                                                 |

|                        | 3:2 | FTRP[1:0] | 00      | PREGAIN control for FRONTR<br>tone control channel<br>00 = 0dB Attenuation<br>01 = -6dB Attenuation<br>10 = -12dB Attenuation<br>11 = -18dB Attenuation                                                          |

|                        | 5:4 | FTLP[1:0] | 00      | PREGAIN control for FRONTL<br>tone control channel<br>00 = 0dB Attenuation<br>01 = -6dB Attenuation<br>10 = -12dB Attenuation<br>11 = -18dB Attenuation                                                          |

|                        | 6   | UPDATEC   | 0       | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store PREGAIN CNTR in<br>intermediate latch (no change to<br>output)<br>1 = Store PREGAIN CNTR and<br>update attenuation on all<br>channels.   |

|                        | 7   | UPDATER   | 0       | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store PREGAIN RIGHT in<br>intermediate latch (no change to<br>output)<br>1 = Store PREGAIN RIGHT and<br>update attenuation on all<br>channels. |

|                        | 8   | UPDATEL   | 0       | Controls simultaneous update of<br>all Attenuation Latches<br>0 = Store PREGAIN LEFT in<br>intermediate latch (no change to<br>output)<br>1 = Store PREGAIN LEFT and<br>update attenuation on all<br>channels.   |

Table 6 Mixer Pre-Gain Registers

#### **BASS MANAGEMENT**

Support is provided for Bass Management in the analogue domain. This might be used either in the case where a partnering DSP has insufficient MIPs to support all required functions, or where an analogue multi-channel input is required to be processed for use with 'small' bass-limited speakers.

Provision is made for single pole high pass filtering of each front, centre, surround or rear channel, using a single external capacitor. The value of this capacitor may be chosen to set the required highpass corner frequency, typically the Dolby recommended 100Hz value being preferred. Use of extra external FET switches would allow the system builder to adjust this corner frequency in the system.

To create the subwoofer channel signal, each of up to all 6 channels is summed into the LFE channel using external discrete summing resistors, and the entire summed subwoofer signal then low-pass band-limited using a further user selectable external capacitor value. This allows the gain from each individual channel, and the overall bass corner response to be selected. Following this summing stage, an integrated volume control allows the overall level of the subwoofer channel to be set.

Figure 3 Bass Management Configuration

#### **BASS MANAGEMENT BYPASS**

Signal paths are provided for the surround and auxiliary channels which allow the user to bypass the high pass filtering operation and apply the unfiltered signals directly to the analogue volume controls.

| REGISTER ADDRESS | BIT | LABEL   | DEFAULT | DESCRIPTION                                |

|------------------|-----|---------|---------|--------------------------------------------|

| (27h)            | 0   | AUXLBYP | 0       | Bypass select for AUX left output          |

| Bass Management  |     |         |         | 0 = Bass managed                           |

| Bypass           |     |         |         | 1 = Bypass                                 |

|                  | 1   | AUXRBYP | 0       | Bypass select for AUX right<br>output      |

|                  |     |         |         | 0 = Bass managed                           |

|                  |     |         |         | 1 = Bypass                                 |

|                  | 2   | SURLBYP | 0       | Bypass select for surround left<br>output  |

|                  |     |         |         | 0 = Bass managed                           |

|                  |     |         |         | 1 = Bypass                                 |

|                  | 3   | SURRBYP | 0       | Bypass select for surround right<br>output |

|                  |     |         |         | 0 = Bass managed                           |

|                  |     |         |         | 1 = Bypass                                 |

Table 7 Bass Management Bypass Register

### **HEADPHONE OUTPUT**

A stereo headphone output is provided which may be used to buffer out either the front L/R channels, or the AUX L/R channels as required. Control is via the HPSEL bit. An independent volume control is provided for this output.

| REGISTER ADDRESS       | BIT | LABEL | DEFAULT | DESCRIPTION                                                                                  |

|------------------------|-----|-------|---------|----------------------------------------------------------------------------------------------|

| (25h)                  | 6   | HPSEL | 0       | Controls headphone output MUX:-                                                              |

| Centre Mixer Control 1 |     |       |         | 0 = FRONT L/R output on<br>headphone channels<br>1 = AUX L/R output on headphone<br>channels |

Table 8 Headphone Source Select

## **OUTPUT POWERDOWN**

The analogue output signal paths are all disabled by default and can be controlled by writing to the appropriate software control register.

| REGISTER ADDRESS | BIT | LABEL  | DEFAULT | DESCRIPTION                       |

|------------------|-----|--------|---------|-----------------------------------|

| (2Dh)            | 0   | AUXLPD | 1       | Auxiliary left output powerdown.  |

| Output Powerdown |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 1   | AUXRPD | 1       | Auxiliary right output powerdown. |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 2   | SURLPD | 1       | Surround left output powerdown.   |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 3   | SURRPD | 1       | Surround Right output             |

|                  |     |        |         | powerdown.                        |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 4   | LFEPD  | 1       | LFE output powerdown.             |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 5   | CTRPD  | 1       | Center output powerdown.          |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 6   | FRTLPD | 1       | Front Left output powerdown.      |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 7   | FRTRPD | 1       | Front Right output powerdown.     |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

|                  | 8   | HPPD   | 1       | Headphone output powerdown.       |

|                  |     |        |         | 0 = enabled                       |

|                  |     |        |         | 1 = disabled                      |

Table 9 Output Powerdown Register

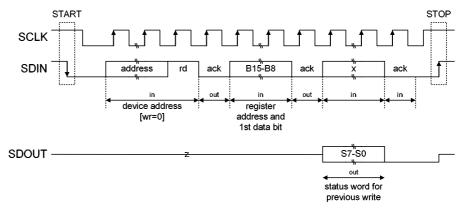

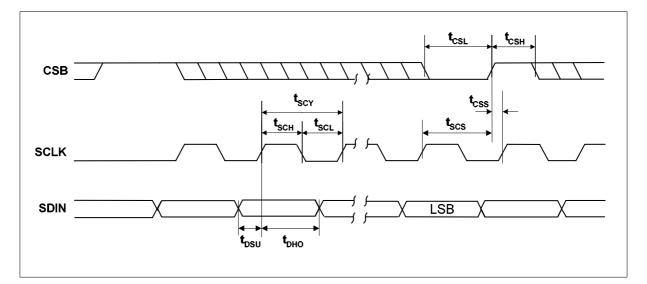

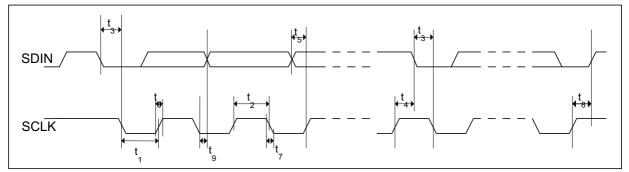

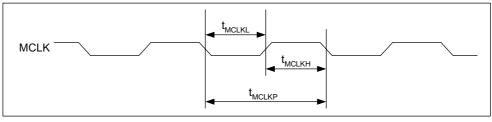

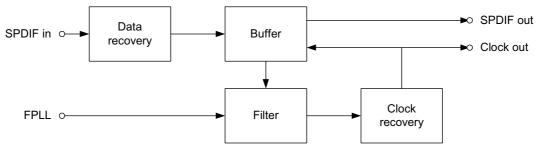

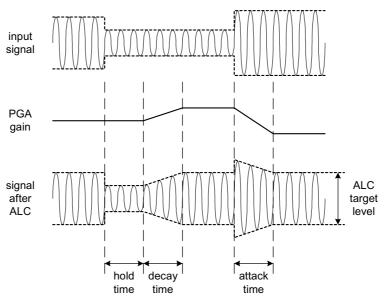

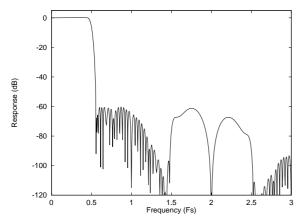

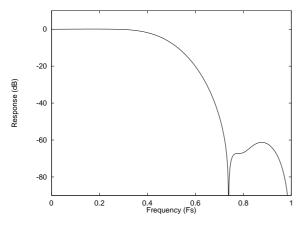

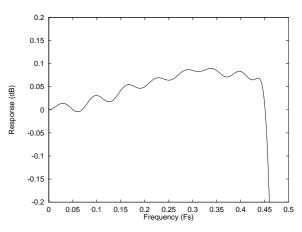

### DIGITAL AUDIO INTERFACE ROUTING OPTIONS